Confidential for

GEAC only

**datasheet**

PRELIMINARY SPECIFICATION

1/2.9" color CMOS 2 megapixel image sensor

OS02G10

**Copyright © 2020 OmniVision Technologies, Inc. All rights reserved.**

This document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample.

OmniVision Technologies, Inc. and all its affiliates disclaim all liability, including liability for infringement of any proprietary rights, relating to the use of information in this document. No license, expressed or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

The information contained in this document is considered proprietary to OmniVision Technologies, Inc. and all its affiliates. This information may be distributed to individuals or organizations authorized by OmniVision Technologies, Inc. to receive said information. Individuals and/or organizations are not allowed to re-distribute said information.

OmniVision products are tested to comply with internal quality testing processes. OmniVision products are not designed or tested for fail-safe performance, including for use in Class III Medical Devices or other critical applications that could lead to death or personal injury. Buyers are advised to perform their own final characterization, testing and certification for use of OmniVision products in any critical application or medical device application. Buyer assumes sole risk and liability for use of OmniVision products in critical applications.

**Trademark Information**

OmniVision and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc.

All other trademarks used herein are the property of their respective owners.

**color CMOS 2 megapixel image sensor**

datasheet (CSP)

PRELIMINARY SPECIFICATION

version 1.11

october 2020

To learn more about OmniVision Technologies, visit [www.ovt.com](http://www.ovt.com).

## applications

- security surveillance systems

- IP cameras

- HD analog cameras

## ordering information

- OS02G10-A41A-001A-Z (color, lead-free)

41-pin CSP

## features

- programmable controls: frame rate, mirror and flip, cropping, and windowing

- supports 2x2 color binning function

- supports output formats: 12-bit/10-bit RAW RGB

- SCCB control interface for register programming

- supports MIPI 2-lane serial output interface

- supports DVP 12-bit output interface

- supports image sizes:

1920 x 1080 @ 30 fps

- supports automatic black level calibration

- supports multi-camera synchronous function

## key specifications (typical)

- **active array size:** 1920 x 1080

- **power supply:**

- analog: 2.8V

- I/O: 1.8V

- core: 1.5V

- **power requirements:** (see **sidebar note**)

- active: TBD

- standby: TBD

- **temperature range:**

- operating: -30°C to +85°C junction temperature (see **table 6-2**)

- stable image: -20°C to +60°C junction temperature (see **table 6-2**)

- **output interfaces:** MIPI 2-lane/DVP 12-bit

- **output formats:** RAW RGB

- **lens size:** 1/2.9"

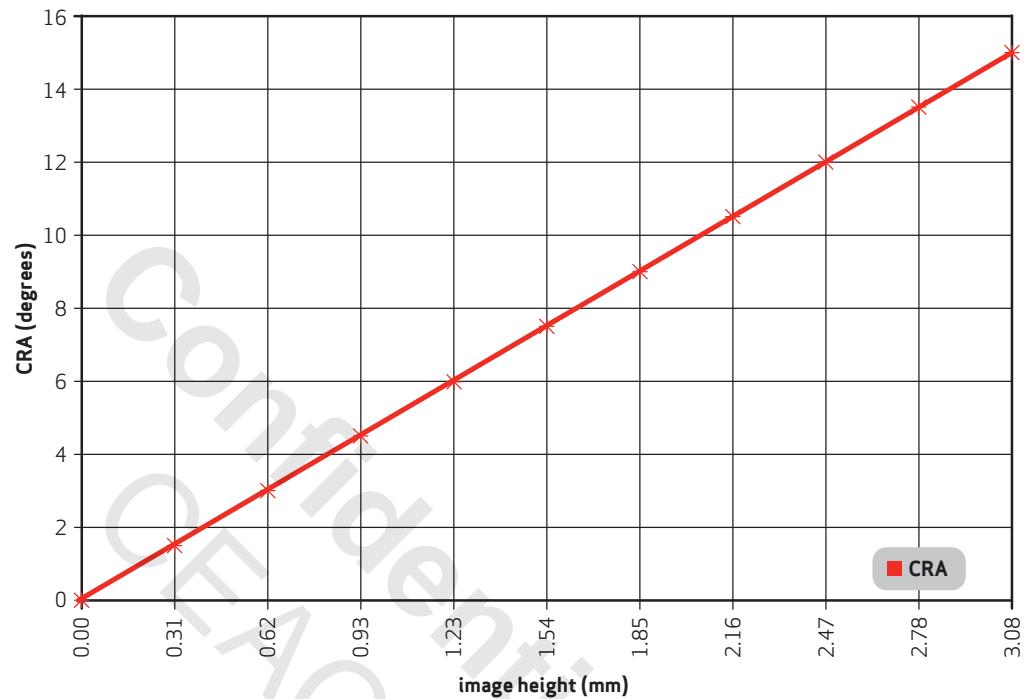

- **lens chief ray angle:** 15° linear (see **figure 8-3**)

- **input clock frequency:** 10~36 MHz

- **maximum image transfer rate:**

1920 x 1080: 30 fps

- **sensitivity:** TBD

- **shutter:** rolling

- **max S/N ratio:** TBD

- **dynamic range:** TBD

- **pixel size:** 2.8 μm x 2.8 μm

- **image area:** 6417 μm x 4145 μm

- **package dimensions:** 6451 μm x 4179 μm

**note** Power requirements specifications are estimated values and are subject to change when measured data using real silicon is available.

OS02G10

color CMOS 2 megapixel image sensor

Confidential for

CEAC only

## table of contents

|                                               |            |

|-----------------------------------------------|------------|

| <b>1 signal descriptions</b>                  | <b>1-1</b> |

| <b>2 system level description</b>             | <b>2-1</b> |

| 2.1 overview                                  | 2-1        |

| 2.2 architecture                              | 2-1        |

| 2.3 format and frame                          | 2-5        |

| 2.4 readout drive mode                        | 2-5        |

| 2.5 I/O control                               | 2-6        |

| 2.6 MIPI interface                            | 2-7        |

| 2.6.1 function related register configuration | 2-7        |

| 2.6.2 D_PHY related register configuration    | 2-8        |

| 2.7 reset                                     | 2-9        |

| 2.7.1 power on reset generation               | 2-9        |

| 2.7.2 software reset                          | 2-9        |

| 2.8 system clock control                      | 2-9        |

| 2.8.1 MPLL (MIPI_PLL)                         | 2-9        |

| 2.8.2 clock configuration                     | 2-9        |

| 2.8.3 PLL clock scheme                        | 2-11       |

| 2.9 power management                          | 2-11       |

| 2.10 data lane parameters                     | 2-12       |

| 2.11 clock lane parameters                    | 2-14       |

| 2.12 power up/off sequence                    | 2-15       |

| 2.12.1 power up sequence                      | 2-15       |

| 2.12.2 power off sequence                     | 2-16       |

| 2.13 SCCB bus                                 | 2-17       |

| 2.13.1 single read and single write           | 2-17       |

| 2.13.2 data bit transfer                      | 2-18       |

| 2.13.3 acknowledge bit                        | 2-18       |

| 2.13.4 data valid                             | 2-18       |

| 2.13.5 timing parameter                       | 2-19       |

| <b>3 block level description</b>              | <b>3-1</b> |

| 3.1 pixel array structure                     | 3-1        |

| 3.2 binning                                   | 3-2        |

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| <b>4 image sensor core digital functions</b>                              | <b>4-1</b> |

| 4.1 mirror and flip                                                       | 4-1        |

| 4.2 windowing                                                             | 4-2        |

| 4.3 test pattern                                                          | 4-3        |

| 4.4 shutter and integration time settings and continuous exposure control | 4-3        |

| 4.4.1 exposure/gain control                                               | 4-4        |

| 4.4.2 HTS/VTS                                                             | 4-4        |

| 4.5 FSIN                                                                  | 4-5        |

| 4.5.1 FSIN common control                                                 | 4-6        |

| 4.6 auto black level calibration (ABLC)                                   | 4-7        |

| 4.6.1 obtaining black level                                               | 4-7        |

| 4.6.2 trigger mode                                                        | 4-8        |

| 4.7 one-time programmable (OTP) memory                                    | 4-9        |

| 4.7.1 batch mode                                                          | 4-9        |

| 4.7.2 single mode                                                         | 4-10       |

| <b>5 register tables</b>                                                  | <b>5-1</b> |

| 5.1 system [P0:0x02 - P0:0x51, P0:0xE7, P0:0xFD]                          | 5-1        |

| 5.2 sensor_ctrl [P1:0x01 - P1:0x4F, P1:0x8E - P1:0xCB, P1:0xDD - P1:0xFB] | 5-5        |

| 5.3 ISP [P2:0x2F - P2:0x5F, P2:0xA0 - P2:0xA7, P2:0xF9 - P2:0xFA]         | 5-13       |

| 5.4 DAC code [P3:0xE]                                                     | 5-15       |

| 5.5 OTP [P6:0x00 - P6:0x2F, P6:0xFD]                                      | 5-15       |

| <b>6 operating specifications</b>                                         | <b>6-1</b> |

| 6.1 absolute maximum ratings                                              | 6-1        |

| 6.2 functional temperature                                                | 6-1        |

| 6.3 DC characteristics                                                    | 6-2        |

| 6.4 timing characteristics                                                | 6-3        |

| <b>7 mechanical specifications</b>                                        | <b>7-1</b> |

| 7.1 physical specifications                                               | 7-1        |

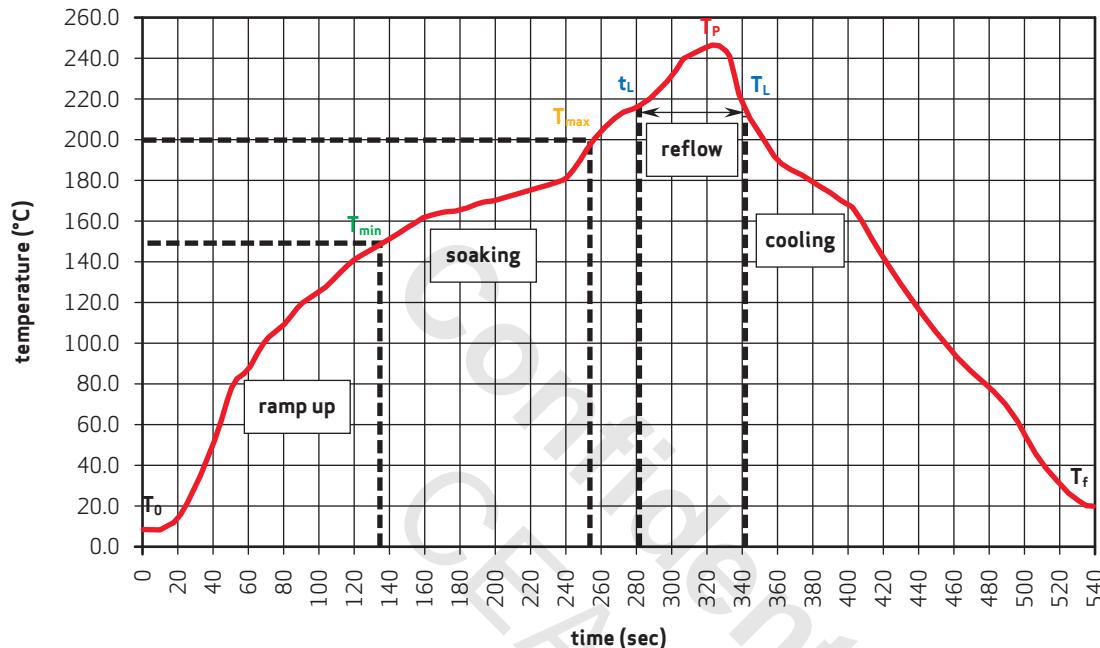

| 7.2 IR reflow specifications                                              | 7-3        |

| 7.3 PCB and SMT design recommendations                                    | 7-4        |

| 7.3.1 PCB design recommendations                                          | 7-4        |

| 7.3.2 SMT design recommendations                                          | 7-5        |

| <b>8 optical specifications</b>                                           | <b>8-1</b> |

| 8.1 sensor array center                                                   | 8-1        |

| 8.2 lens chief ray angle (CRA)                                            | 8-2        |

## list of figures

|             |                                                                        |      |

|-------------|------------------------------------------------------------------------|------|

| figure 1-1  | pin diagram                                                            | 1-1  |

| figure 2-1  | OS02G10 block diagram                                                  | 2-2  |

| figure 2-2  | OS02G10 DVP reference schematic                                        | 2-3  |

| figure 2-3  | OS02G10 MIPI reference schematic                                       | 2-4  |

| figure 2-4  | PLL internal function block diagram                                    | 2-11 |

| figure 2-5  | high-speed data transmission bursts                                    | 2-12 |

| figure 2-6  | switching the clock lane between clock transmission and low-power mode | 2-12 |

| figure 2-7  | power up sequence diagram                                              | 2-15 |

| figure 2-8  | power off sequence diagram                                             | 2-16 |

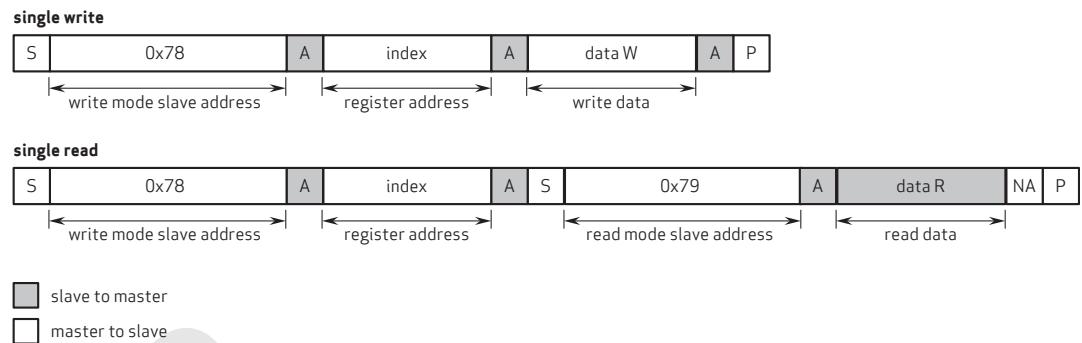

| figure 2-9  | SCCB read and write message description (SID pin set high)             | 2-17 |

| figure 2-10 | SCCB read and write message description (SID pin set low)              | 2-18 |

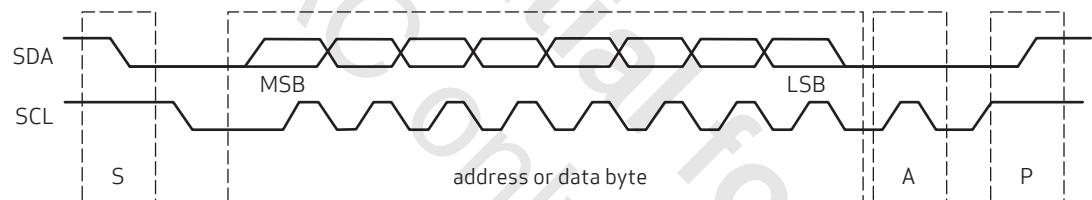

| figure 2-11 | SCCB acknowledge bit diagram                                           | 2-18 |

| figure 2-12 | SCCB data transport diagram                                            | 2-18 |

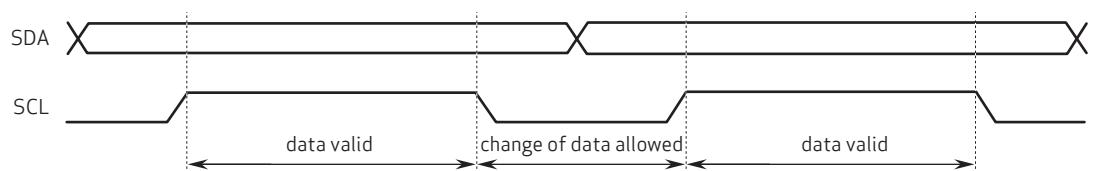

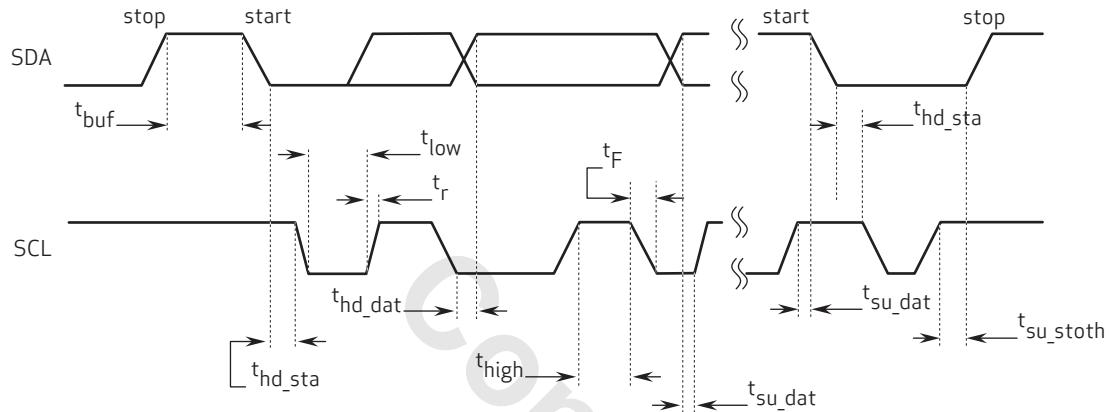

| figure 2-13 | SCCB bus timing parameter diagram                                      | 2-19 |

| figure 3-1  | sensor array region color filter layout                                | 3-1  |

| figure 3-2  | example of 2x2 binning                                                 | 3-2  |

| figure 4-1  | mirror and flip samples                                                | 4-1  |

| figure 4-2  | windowing diagram                                                      | 4-2  |

| figure 4-3  | test pattern diagram                                                   | 4-3  |

| figure 4-4  | shutter and integration time settings and continuous exposure control  | 4-4  |

| figure 4-5  | integration time control within a frame                                | 4-5  |

| figure 6-1  | reference clock input timing diagram                                   | 6-3  |

| figure 7-1  | package specifications                                                 | 7-1  |

| figure 7-2  | IR reflow ramp rate requirements                                       | 7-3  |

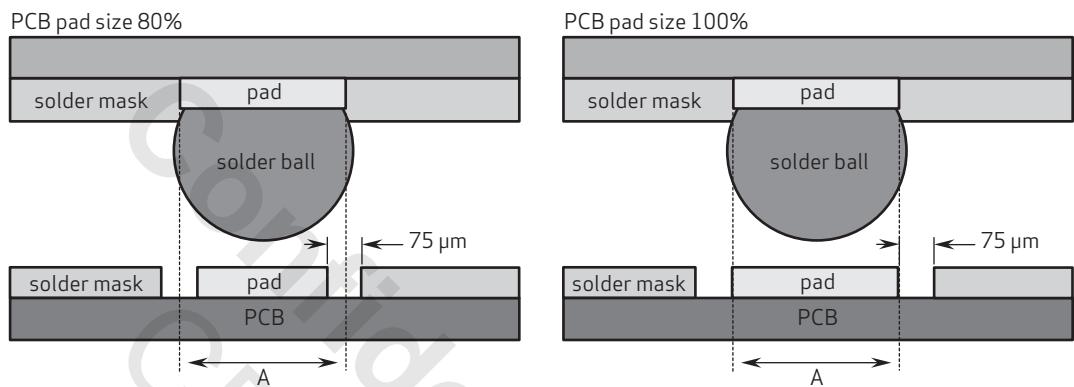

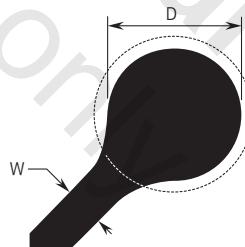

| figure 7-3  | PCB pad example                                                        | 7-4  |

| figure 7-4  | tear drop design example                                               | 7-4  |

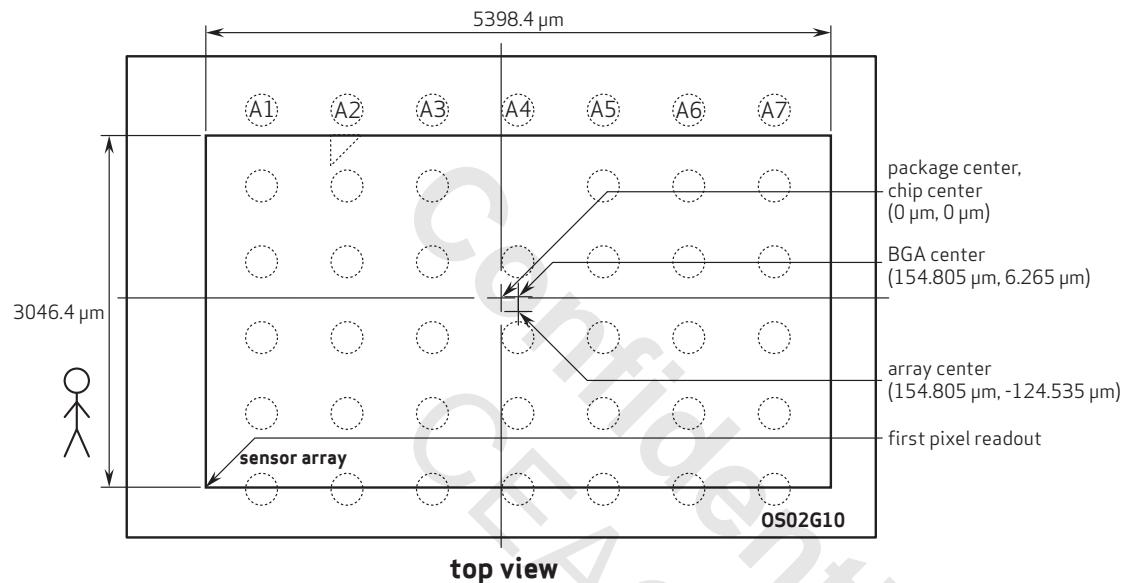

| figure 8-1  | sensor array center                                                    | 8-1  |

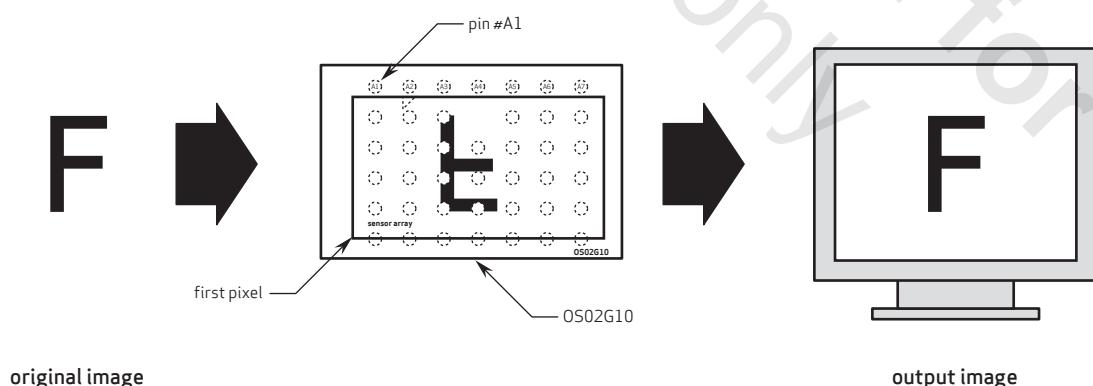

| figure 8-2  | final image output                                                     | 8-1  |

| figure 8-3  | chief ray angle (CRA)                                                  | 8-2  |

OS02G10

color CMOS 2 megapixel image sensor

Confidential for

CEAC only

## list of tables

|            |                                        |      |

|------------|----------------------------------------|------|

| table 1-1  | signal descriptions                    | 1-1  |

| table 1-2  | pin states under various conditions    | 1-3  |

| table 1-3  | pad symbol and equivalent circuit      | 1-4  |

| table 2-1  | formats and frame rates                | 2-5  |

| table 2-2  | operating modes                        | 2-5  |

| table 2-3  | I/O control functions                  | 2-6  |

| table 2-4  | MIPI function related registers        | 2-7  |

| table 2-5  | D_PHY related registers                | 2-8  |

| table 2-6  | clock configuration related registers  | 2-9  |

| table 2-7  | data lane parameters                   | 2-13 |

| table 2-8  | clock lane parameters                  | 2-14 |

| table 2-9  | power up sequence parameters           | 2-15 |

| table 2-10 | power off sequence parameters          | 2-16 |

| table 2-11 | SCCB interface timing specifications   | 2-19 |

| table 3-1  | binning-related register               | 3-2  |

| table 4-1  | mirror and flip registers              | 4-1  |

| table 4-2  | windowing control registers            | 4-2  |

| table 4-3  | FSIN control registers                 | 4-6  |

| table 4-4  | BLC registers                          | 4-7  |

| table 4-5  | BLC statistics register                | 4-8  |

| table 4-6  | BLC offset registers                   | 4-8  |

| table 4-7  | OTP batch mode registers               | 4-9  |

| table 4-8  | OTP single mode registers              | 4-10 |

| table 4-9  | OTP read register                      | 4-11 |

| table 5-1  | system registers                       | 5-1  |

| table 5-2  | sensor_ctrl registers                  | 5-5  |

| table 5-3  | ISP registers                          | 5-13 |

| table 5-4  | DAC code register                      | 5-15 |

| table 5-5  | OTP registers                          | 5-15 |

| table 6-1  | absolute maximum ratings               | 6-1  |

| table 6-2  | functional temperature                 | 6-1  |

| table 6-3  | DC characteristics (-30°C < TJ < 85°C) | 6-2  |

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| table 6-4 timing characteristics                                       | 6-3 |

| table 7-1 package dimensions                                           | 7-1 |

| table 7-2 reflow conditions                                            | 7-3 |

| table 7-3 ball pad opening size and recommended PCB NSMD ball pad size | 7-4 |

| table 8-1 CRA versus image height plot                                 | 8-2 |

Confidential for

CEAC only

# 1 signal descriptions

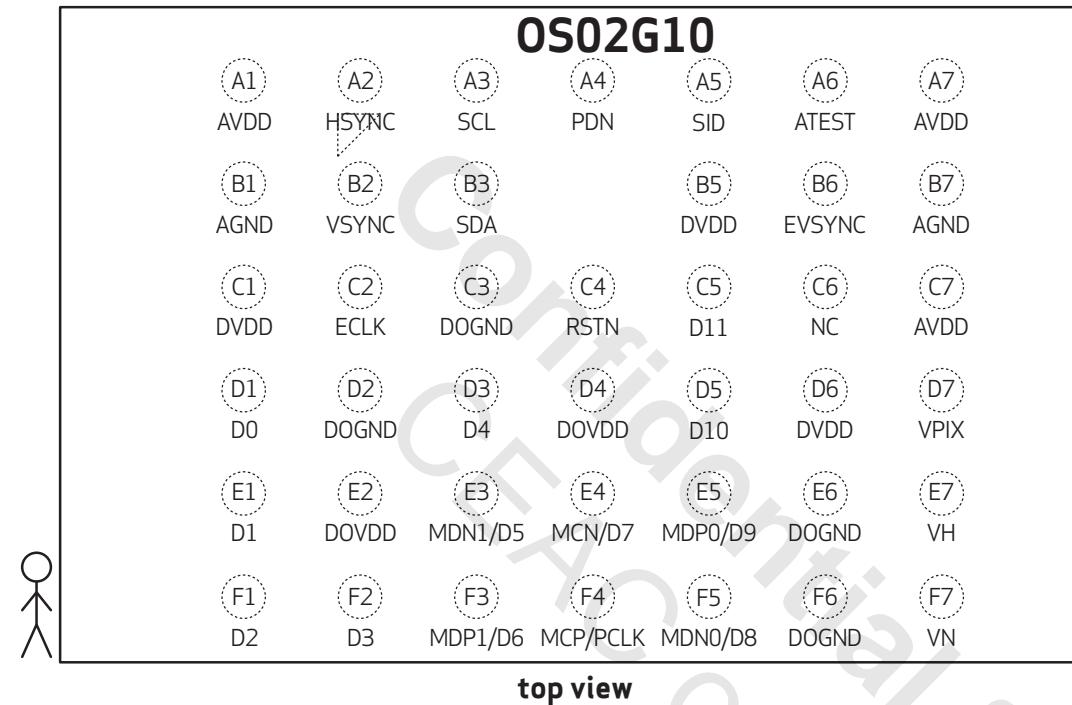

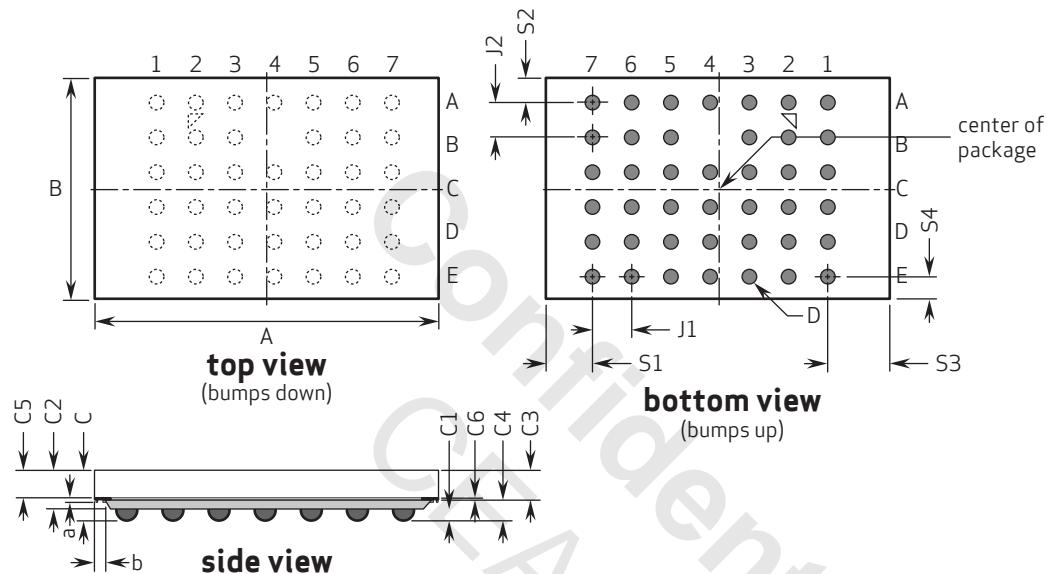

table 1-1 lists the signal descriptions and their corresponding pin numbers for the OS02G10 image sensor. The package information is shown in [section 8](#).

figure 1-1 pin diagram

table 1-1 signal descriptions (sheet 1 of 3)

| pin number | signal name  | pin type | description                               |

|------------|--------------|----------|-------------------------------------------|

| A1         | AVDD         | power    | analog power 2.8V                         |

| A2         | <b>HSYNC</b> | output   | horizontal sync signal                    |

| A3         | <b>SCL</b>   | input    | SCCB clock                                |

| A4         | <b>PDN</b>   | input    | power down<br>0: Enable<br>1: Normal work |

| A5         | <b>SID</b>   | input    | SID control                               |

| A6         | ATEST        | output   | analog test output                        |

table 1-1 signal descriptions (sheet 2 of 3)

| pin number | signal name    | pin type  | description                                              |

|------------|----------------|-----------|----------------------------------------------------------|

| A7         | AVDD           | power     | analog power 2.8V                                        |

| B1         | AGND           | ground    | analog ground                                            |

| B2         | <b>VSYNC</b>   | output    | vertical sync signal                                     |

| B3         | <b>SDA</b>     | I/O       | SCCB data                                                |

| B5         | DVDD           | power     | digital core power 1.5V                                  |

| B6         | <b>EVSYNC</b>  | I/O       | external vertical sync signal                            |

| B7         | AGND           | ground    | analog ground                                            |

| C1         | DVDD           | power     | digital core power 1.5V                                  |

| C2         | <b>ECLK</b>    | input     | external clock input                                     |

| C3         | DOGND          | ground    | digital ground                                           |

| C4         | <b>RSTN</b>    | input     | reset<br>0: Enable<br>1: Normal work                     |

| C5         | <b>D11</b>     | output    | DVP data output 11                                       |

| C6         | NC             | —         | no connect                                               |

| C7         | AVDD           | power     | analog power 2.8V                                        |

| D1         | <b>D0</b>      | output    | DVP data output 0                                        |

| D2         | DOGND          | ground    | digital ground                                           |

| D3         | <b>D4</b>      | output    | DVP data output 4                                        |

| D4         | DOVDD          | power     | digital I/O power 1.8V/2.8V                              |

| D5         | <b>D10</b>     | output    | DVP data output 10                                       |

| D6         | DVDD           | power     | digital core power 1.5V                                  |

| D7         | VPIX           | output    | internal reference (connect to 1μF capacitor outside)    |

| E1         | <b>D1</b>      | output    | DVP data output 1                                        |

| E2         | DOVDD          | power     | digital I/O power 1.8V/2.8V                              |

| E3         | <b>MDN1/D5</b> | output    | MIPI data negative output 1 output and DVP data output 5 |

| E4         | <b>MCN/D7</b>  | output    | MIPI clock negative output and DVP data output 7         |

| E5         | <b>MDP0/D9</b> | output    | MIPI data positive output 0 and DVP data output 9        |

| E6         | DOGND          | ground    | digital ground                                           |

| E7         | VH             | reference | internal reference (connect to 1μF capacitor outside)    |

| F1         | <b>D2</b>      | output    | DVP data output 2                                        |

**table 1-1** signal descriptions (sheet 3 of 3)

| pin number | signal name     | pin type  | description                                                 |

|------------|-----------------|-----------|-------------------------------------------------------------|

| F2         | <b>D3</b>       | output    | DVP data output 3                                           |

| F3         | <b>MDP1/D6</b>  | output    | MIPI data positive output 1 and DVP data output 6           |

| F4         | <b>MCP/PCLK</b> | output    | MIPI clock positive output and pixel output clock           |

| F5         | <b>MDN0/D8</b>  | output    | MIPI data negative output 0 and DVP data output 8           |

| F6         | DOGND           | ground    | digital ground                                              |

| F7         | VN              | reference | internal reference (connect to 1 $\mu$ F capacitor outside) |

**table 1-2** pin states under various conditions (sheet 1 of 2)

| pin number | signal name | PDN = 0 | PDN = 1; RSTN = 0 | PDN = 1; RSTN = 1                |

|------------|-------------|---------|-------------------|----------------------------------|

| <b>A2</b>  | HSYNC       | high-z  | high-z            | high-z by default (configurable) |

| <b>A3</b>  | SCL         | high-z  | input             | input                            |

| <b>A4</b>  | PDN         | input   | input             | input                            |

| <b>A5</b>  | SID         | input   | input             | input                            |

| <b>B2</b>  | VSYNC       | high-z  | high-z            | high-z by default (configurable) |

| <b>B3</b>  | SDA         | high-z  | high-z            | I/O                              |

| <b>B6</b>  | EVSYNC      | high-z  | high-z            | I/O (configurable)               |

| <b>C2</b>  | ECLK        | input   | input             | input                            |

| <b>C4</b>  | RSTN        | input   | input             | input                            |

| <b>C5</b>  | D11         | high-z  | high-z            | high-z by default (configurable) |

| <b>D1</b>  | D0          | high-z  | high-z            | high-z by default (configurable) |

| <b>D3</b>  | D4          | high-z  | high-z            | high-z by default (configurable) |

| <b>D5</b>  | D10         | high-z  | high-z            | high-z by default (configurable) |

| <b>E1</b>  | D1          | high-z  | high-z            | high-z by default (configurable) |

| <b>E3</b>  | MDN1/D5     | high-z  | high-z            | high-z by default (configurable) |

| <b>E4</b>  | MCN/D7      | high-z  | high-z            | high-z by default (configurable) |

| <b>E5</b>  | MDP0/D9     | high-z  | high-z            | high-z by default (configurable) |

| <b>F1</b>  | D2          | high-z  | high-z            | high-z by default (configurable) |

| <b>F2</b>  | D3          | high-z  | high-z            | high-z by default (configurable) |

**table 1-2** pin states under various conditions (sheet 2 of 2)

| pin number | signal name | PDN = 0 | PDN = 1; RSTN = 0 | PDN = 1; RSTN = 1                |

|------------|-------------|---------|-------------------|----------------------------------|

| <b>F3</b>  | MDP1/D6     | high-z  | high-z            | high-z by default (configurable) |

| <b>F4</b>  | MCP/PCLK    | high-z  | high-z            | high-z by default (configurable) |

| <b>F5</b>  | MDN0/D8     | high-z  | high-z            | high-z by default (configurable) |

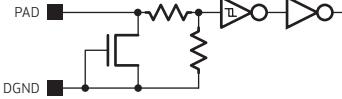

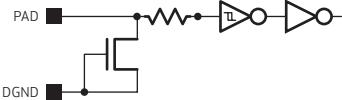

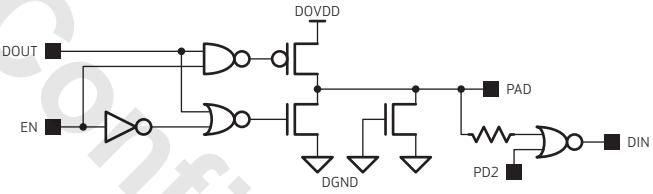

**table 1-3** pad symbol and equivalent circuit (sheet 1 of 2)

| symbol                                                                             | equivalent circuit |

|------------------------------------------------------------------------------------|--------------------|

| D0, D1, D2, D3, D4, MDN1/D5, MDP1/D6, MCN/D7, MCP/PCLK, MDN0/D8, MDP0/D9, D10, D11 |                    |

| AGND, DGND, VPIX, ATEST, VH                                                        |                    |

| VN                                                                                 |                    |

| AVDD, DVDD, DOVDD                                                                  |                    |

| ECLK                                                                               |                    |

| SDA                                                                                |                    |

**table 1-3** pad symbol and equivalent circuit (sheet 2 of 2)

| symbol    | equivalent circuit                                                                 |

|-----------|------------------------------------------------------------------------------------|

| RSTN, PDN |   |

| SCL       |   |

| EVSYNC    |  |

OS02G10

color CMOS 2 megapixel image sensor

Confidential for

CEAC only

## 2 system level description

### 2.1 overview

The OS02G10 image sensor is a high quality, 1/2.9 inch, 1080p format, CMOS image sensor. It provides high quality digital images and high-definition (HD) video. The OS02G10 focuses on products including security surveillance systems, IP cameras and HD analog cameras.

By introducing an advanced 2.8  $\mu$ m pixel architecture, the OS02G10 achieves excellent low-light sensitivity, signal-to-noise ratio, full-well capacity, quantum efficiency and low-power consumption. The default mode and programmable mode allow for a more convenient way of controlling the parameters of frame size, exposure time, gain value, etc. It also offers the following image control functions: mirror and flip, windowing, auto black level calibration, defective pixel correction, black sun cancellation, and other functions.

The OS02G10 supports a high frame rate of up to 30 fps @ 1080p format through the DVP interface or MIPI interface. These prominent features integrated in the OS02G10 allow for a best-in-class image sensor that will bring users vivid pictures and an excellent experience.

### 2.2 architecture

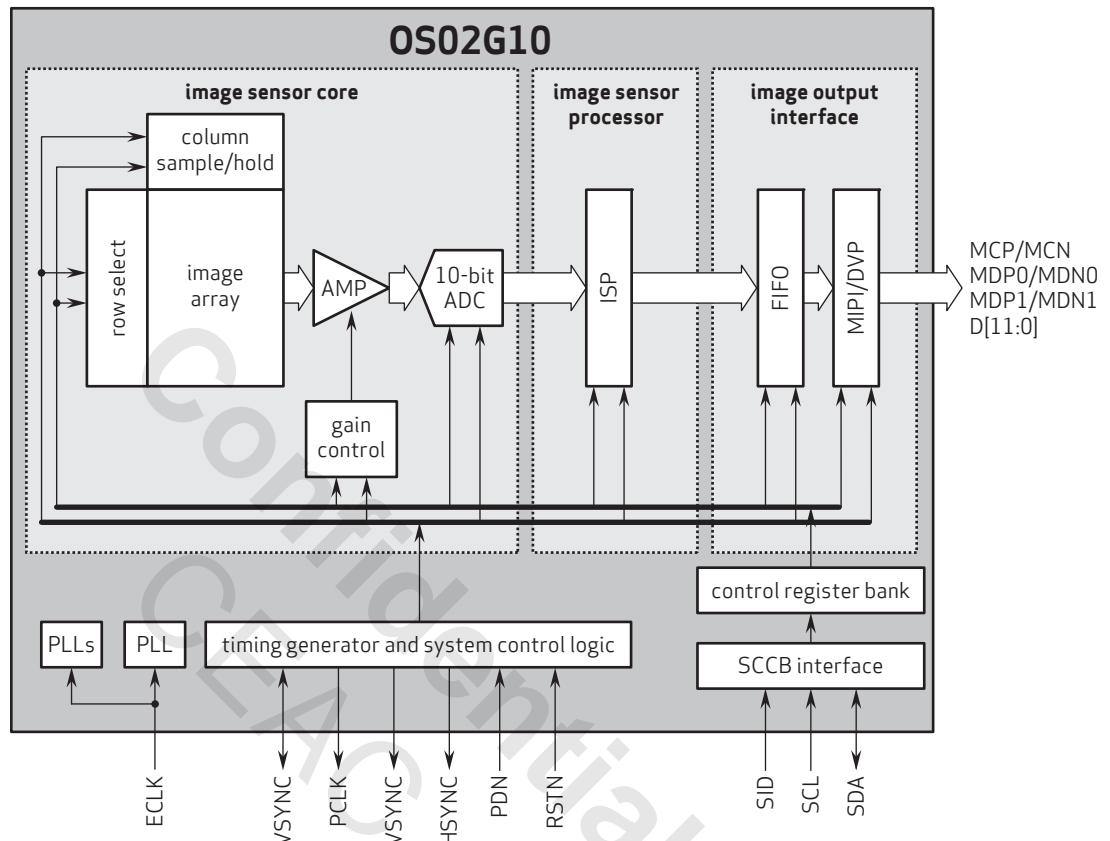

The OS02G10 sensor core generates streaming pixel data at a constant frame rate. **figure 2-1** shows the functional block diagram of the OS02G10 image sensor.

The timing generator outputs clocks to access the rows of the imaging array, pre-charging and sampling the rows of the array sequentially. In the time between pre-charging and sampling a row, the charge in the pixels decreases with exposure to incident light. This is the exposure time in rolling shutter architecture.

The exposure time is controlled by adjusting the time interval between pre-charging and sampling. After the data of the pixels in the row has been sampled, it is processed through analog circuitry to correct the offset and multiply the data with corresponding gain. Following analog processing is the ADC which outputs up to 10-bit data for each pixel in the array.

figure 2-1 OS02G10 block diagram

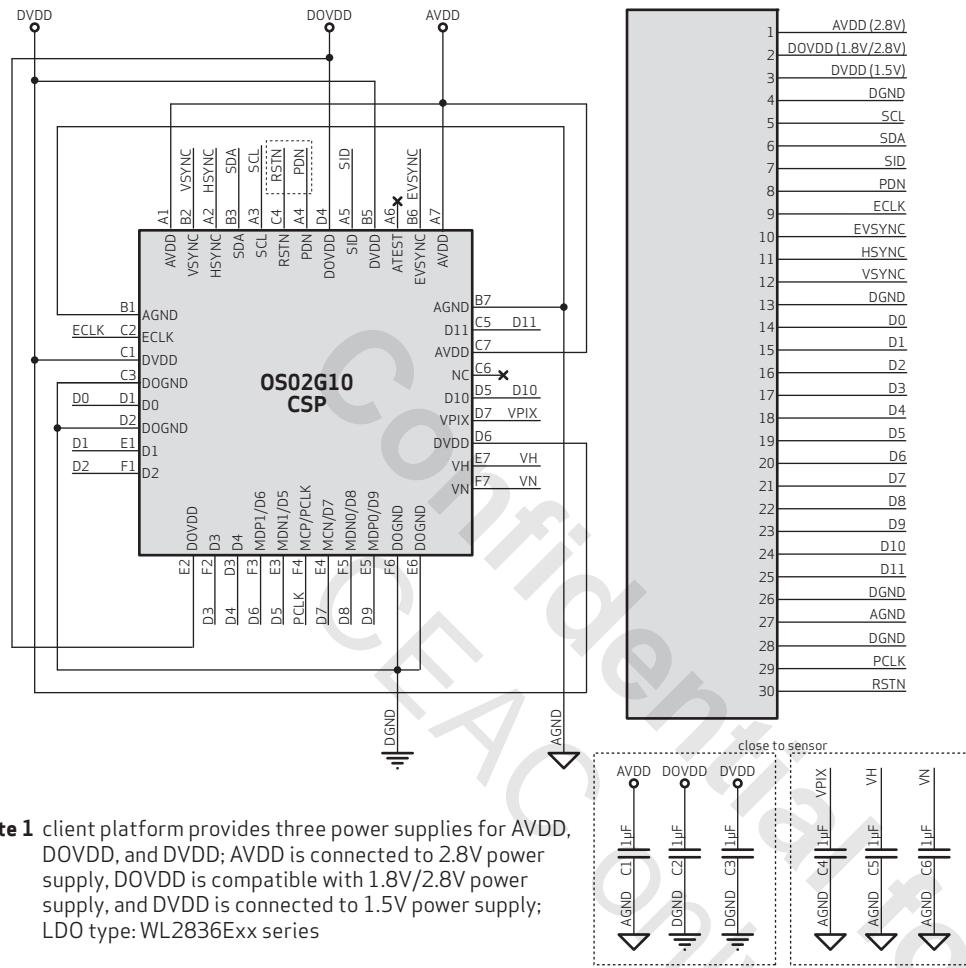

figure 2-2 OS02G10 DVP reference schematic

**note 1** client platform provides three power supplies for AVDD, DOVDD, and DVDD; AVDD is connected to 2.8V power supply, DOVDD is compatible with 1.8V/2.8V power supply, and DVDD is connected to 1.5V power supply; LDO type: WL2836Exx series

**note 2** when platform GPIO pin is limited, PDN must be controlled by platform GPIO; RSTN can be directly connected to DOVDD

**note 3** this design is for parallel port mode, where MDN1/D5, MDP1/D6, MDN0/D8, MDP0/D9, MCN/D7, and MCN/PCLK are multiplexed pins, and are used as D5, D6, D8, D9, D7 and PCLK; SID is SCCB address controllable pin; when SID is connected low, write address is 0x78 and read address is 0x79; when SID is connected high, write address is 0x7A and read address is 0x7B

**note 4** in PCB design, place chip power filter capacitors close to power pins; place 1  $\mu$ F capacitors near AVDD, DOVDD, DVDD, VPIX, VH, VN in module; AGND and DGND of sensor should be separated inside module and outside PCB single-point connection; AVDD and AGND should not be adjacent to clock; power supply should be designed as thin as 0.12 mm as much as possible, and bottom line should be pulled to ground

**note 5** FPC using anti-jamming design

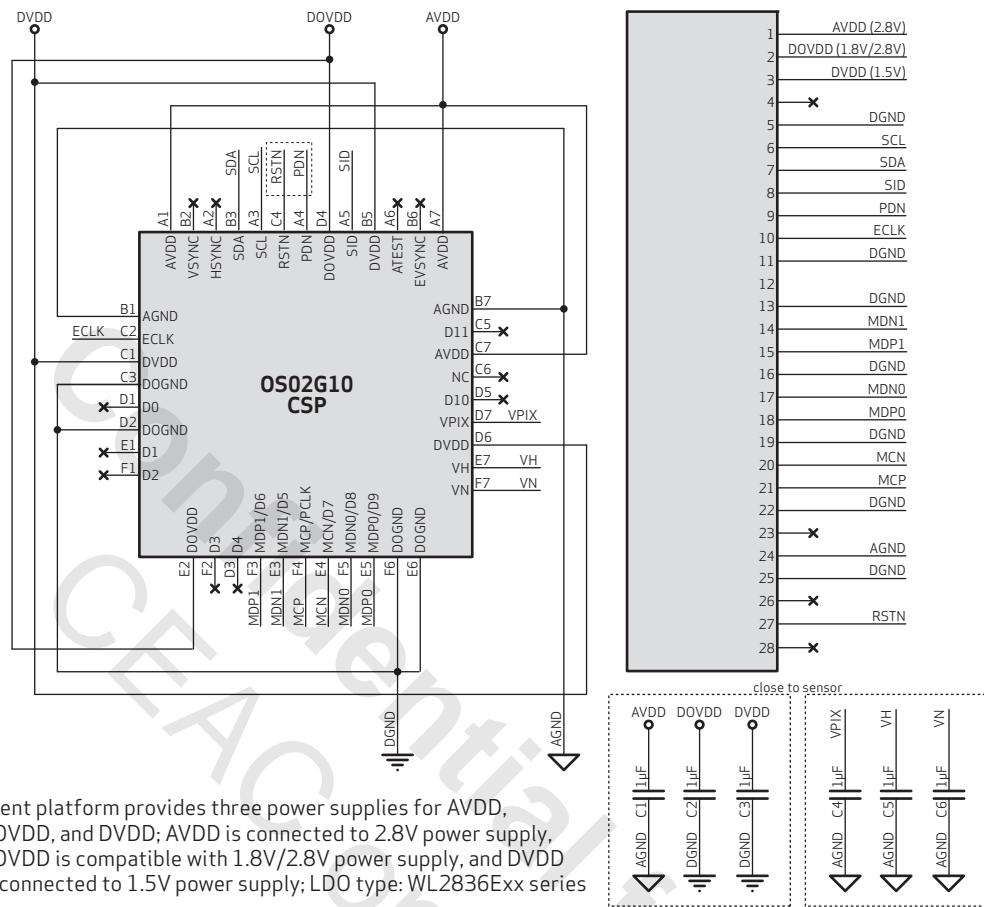

figure 2-3 OS02G10 MIPI reference schematic

**note 1** client platform provides three power supplies for AVDD, DOVDD, and DVDD; AVDD is connected to 2.8V power supply, DOVDD is compatible with 1.8V/2.8V power supply, and DVDD is connected to 1.5V power supply; LDO type: WL2836Exx series

**note 2** when platform GPIO pin is limited, PDN must be controlled by platform GPIO; RSTN can be directly connected to DOVDD

**note 3** this design is for MIPI mode, where MDN1/D5, MDP1/D6, MDN0/D8, MDP0/D9, MCN/D7, and MCN/PCLK are multiplexed pins, and are used as MDN1, MDP1, MDN0, MDP0, and MCN and MCP; SID is SCCB address controllable pin; when SID is connected low, write address is 0x78 and read address is 0x79; when SID is connected high, write address is 0x7A and read address is 0x7B

**note 4** in PCB design, place chip power filter capacitors close to power pins; place 1  $\mu$ F capacitors near AVDD, DOVDD, DVDD, VPIX, VH, VN in module; AGND and DGND of sensor should be separated inside module and outside PCB single-point connection; AVDD and AGND should not be adjacent to clock; power supply should be designed as thin as 0.12 mm as much as possible, and bottom line should be pulled to ground

**note 5** MCN/MCP, MDN0/MDP0, and MDN1/MDP1 are three pairs of differential lines; traces should be wrapped as long as possible with equal spacing; bottom layer (or top layer) of differential lines must have a complete reference ground; for PCB manufacturers to distinguish which are differential lines, manufacturers need to perform impedance control during production; impedance standard is 100 ohm, and error cannot exceed  $\pm 10\%$

**note 6** FPC using anti-jamming design

## 2.3 format and frame

The OS02G10 supports RAW RGB output with a 2-lane MIPI interface.

**table 2-1** formats and frame rates

| format  | resolution  | frame rate | methodology                                               | 10-bit output<br>MIPI data rate      | DVP<br>pixel clock |

|---------|-------------|------------|-----------------------------------------------------------|--------------------------------------|--------------------|

| 1080p   | 1920 x 1080 | 30 fps     | full resolution<br>qualified pixel<br>(1920+8) x (1080+8) | 2-lane @720 Mbps/lane<br>10-bit MIPI | 36 MHz x 2         |

| binning | 968 x 548   | 60 fps     | binning<br>qualified pixel<br>(960+4) x (540+4)           | 2-lane @720 Mbps/lane<br>10-bit MIPI | 36 MHz x 2         |

| 720p    | 1280 x 720  | 60 fps     | crop from full resolution                                 | 2-lane @720 Mbps/lane<br>10-bit MIPI | 42 MHz x 2         |

## 2.4 readout drive mode

**table 2-2** lists the operating modes available with the OS02G10 sensor.

**table 2-2** operating modes

| drive mode | timer clock (MHz) | frame rate (fps) | output resolution (bit) | data rate (Mpixels/s) | number of effective pixels |           | data width                        |                                   | 1H period (s)         |

|------------|-------------------|------------------|-------------------------|-----------------------|----------------------------|-----------|-----------------------------------|-----------------------------------|-----------------------|

|            |                   |                  |                         |                       | H (pixels)                 | V (lines) | H (timer_clk)                     | V (lines)                         |                       |

| full res   | 42                | 30               | 10                      | 84                    | 1928                       | 1088      | ROWTIME<br>(P1:0x41,<br>P1:0x42}) | FRMTIME<br>(P1:0x4E,<br>P1:0x4F}) | ROWTIME<br>/timer_clk |

| binning    | 42                | 60               | 10                      | 42                    | 964                        | 544       | ROWTIME<br>(P1:0x41,<br>P1:0x42}) | FRMTIME<br>(P1:0x4E,<br>P1:0x4F}) | ROWTIME<br>/timer_clk |

| 720p       | 42                | 60               | 10                      | 84                    | 1288                       | 728       | ROWTIME<br>(P1:0x41,<br>P1:0x42}) | FRMTIME<br>(P1:0x4E,<br>P1:0x4F}) | ROWTIME<br>/timer_clk |

| VGA        | 42                | 60               | 10                      | 42                    | 648                        | 488       | ROWTIME<br>(P1:0x41,<br>P1:0x42}) | FRMTIME<br>(P1:0x4E,<br>P1:0x4F}) | ROWTIME<br>/timer_clk |

## 2.5 I/O control

Some I/O pads of the OS02G10 sensor can be configured as inputs or outputs.

**table 2-3** I/O control functions

| function                                                                                 | register | description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK_INV_BUF,<br>EVSYNC_OE_BUF,<br>EVSYNC_IE_OUT_END_BUF,<br>OUT_ENS_BUF,<br>OUT_ENP_BUF | P0:0x1B  | <p>Bit[5]: pclk_inv_buf<br/>PCLK reverse enable<br/>0: Disable PCLK reverse<br/>1: Enable PCLK reverse</p> <p>Bit[4]: evsync_oe_buf<br/>Pad EVSYNC output enable signal<br/>0: Enable output<br/>1: Disable output</p> <p>Bit[3]: evsync_ie<br/>Pad EVSYNC input enable signal<br/>0: Enable output<br/>1: Disable output</p> <p>Bit[2]: out_end_buf<br/>Pad DATAOUT[9:0] output enable signal<br/>0: Enable output<br/>1: Disable output</p> <p>Bit[1]: out_ens_buf<br/>Pad VSYNC and HSYNC output enable signal<br/>0: Enable output<br/>1: Disable output</p> <p>Bit[0]: out_enp_buf<br/>Pad PCLK output enable signal<br/>0: Enable output<br/>1: Disable output</p> |

| DS_DATA, DS_PCLK,<br>DS_HSYNC, DS_VSYNC                                                  | P0:0x1E  | <p>Bit[7:6]: ds_vsync<br/>Driver current select signal of pad VSYNC</p> <p>Bit[5:4]: ds_hsync<br/>Driver current select signal of pad HSYNC</p> <p>Bit[3:2]: ds_pclk<br/>Driver current select signal of pad PCLK</p> <p>Bit[1:0]: ds_data<br/>Driver current select signal of pad DATAOUT[9:0]</p>                                                                                                                                                                                                                                                                                                                                                                      |

## 2.6 MIPI interface

The OS02G10 supports a uni-directional two-lane MIPI transmitter interface and is capable of a data transfer rate of up to 840 Mbps. When MIPI works normally, the typical data type is RAW10 and also supports RAW8 data format. The default data transmission is high speed (HS) transfer mode.

### 2.6.1 function related register configuration

**table 2-4** MIPI function related registers (sheet 1 of 2)

| address | register name                           | default value | R/W | description                                                                                                                                             |

|---------|-----------------------------------------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1:0x8E | H_SIZE_MIPI_4MSB                        | 0x07          | RW  | Bit[3:0]: h_size_mipi[11:8]                                                                                                                             |

| P1:0x8F | H_SIZE_MIPI_8LSB                        | 0x88          | RW  | Bit[7:0]: h_size_mipi[7:0]                                                                                                                              |

| P1:0x90 | V_SIZE_MIPI_3MSB                        | 0x04          | RW  | Bit[7:3]: Not used<br>Bit[2:0]: v_size_mipi[10:8]                                                                                                       |

| P1:0x91 | V_SIZE_MIPI_8LSB                        | 0x40          | RW  | Bit[7:0]: v_size_mipi[7:0]                                                                                                                              |

| P1:0x92 | HS_MODE_VF,<br>HS_MODE, LP_CTL          | 0x02          | RW  | Bit[4]: hs_mode_vf<br>0: Clock switch per line<br>1: Clock switch per frame<br>Bit[3]: hs_mode<br>0: Clock burst<br>1: Clock switch<br>Bit[2:0]: lp_ctl |

| P1:0x93 | R_CLK_POST                              | 0x0E          | RW  | Bit[4:0]: r_clk_post                                                                                                                                    |

| P1:0x94 | R_LPC_CK, R_LPC_DAT                     | 0x77          | RW  | Bit[7:4]: r_lpx_ck<br>Bit[3:0]: r_lpx_dat                                                                                                               |

| P1:0x95 | R_CLK_PREPARE,<br>R_HS_PREPARE          | 0x56          | RW  | Bit[7:4]: r_clk_prepare<br>Bit[3:0]: r_hs_prepare                                                                                                       |

| P1:0x96 | R_HS_ZERO                               | 0x1A          | RW  | Bit[4:0]: r_hs_zero                                                                                                                                     |

| P1:0x97 | DATA_ID                                 | 0x2B          | RW  | Bit[7:0]: data_id<br>0x2A: 8-bit mode<br>0x2B: 10-bit mode HSIZE low 8-bit                                                                              |

| P1:0x98 | R_CLK_TRAIL,<br>R_HS_TRAIL              | 0x78          | RW  | Bit[7:4]: r_clk_trail<br>Bit[3:0]: r_hs_trail                                                                                                           |

| P1:0x9C | R_CLK_ZERO                              | 0x22          | RW  | Bit[5:0]: r_clk_zero                                                                                                                                    |

| P1:0xA1 | MIPI_LS_START_NUM,<br>TX_SPEED_AREA_SEL | 0x03          | RW  | Bit[4:3]: miipi_ls_start_num<br>Bit[2:0]: tx_speed_area_sel                                                                                             |

| P1:0xA2 | R_INIT_M                                | 0x0B          | RW  | Bit[7:0]: r_init[15:8]                                                                                                                                  |

| P1:0xA3 | R_INIT_L                                | 0x40          | RW  | Bit[7:0]: r_init[7:0]                                                                                                                                   |

table 2-4 MIPI function related registers (sheet 2 of 2)

| address | register name       | default value | R/W | description                                                                                                                                                            |

|---------|---------------------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1:0xA4 | R_EXIT, R_WAKEUP_MH | 0x10          | RW  | Bit[5:2]: r_exit<br>Bit[1:0]: r_wakeup[17:16]                                                                                                                          |

| P1:0xA5 | R_WAKEUP_M          | 0x86          | RW  | Bit[7:0]: r_wakeup[15:8]                                                                                                                                               |

| P1:0xA6 | R_WAKEUP_L          | 0x88          | RW  | Bit[7:0]: r_wakeup[7:0]                                                                                                                                                |

| P1:0xA7 | DC_TEST_LP_LK       | 0x3F          | RW  | Bit[7]: dc_test_hsdc_en<br>Bit[6]: dc_test_hsdd_en<br>Bit[5:4]: dc_test_lp_ck_en<br>Bit[3:2]: dc_test_lp_d1_en<br>Bit[1:0]: Reserved for data lane's zero time control |

| P1:0xA8 | DC_TEST_DATA_HS     | 0xFF          | RW  | Bit[7:0]: dc_test_data_hs                                                                                                                                              |

| P1:0xAE | FRAME_END_DLY_8LSB  | 0x65          | RW  | Bit[7:0]: frame_end_dly[7:0]                                                                                                                                           |

| P1:0xAF | FRAME_END_DLY_8MSB  | 0x01          | RW  | Bit[7:0]: frame_end_dly[15:8]                                                                                                                                          |

| P1:0xB1 | MIPI_EN, SHUTDOWNA  | 0x00          | RW  | Bit[1]: mipi_en<br>Bit[0]: Shutdowna                                                                                                                                   |

| P1:0xB2 | MIPI_HSYNC_NUM      | 0x96          | RW  | Bit[7:0]: mipi_hsync_num<br>Used in line sync mode                                                                                                                     |

| P1:0xB6 | LS_MODE, LP_SST_EN  | 0x00          | RW  | Bit[4]: ls_mode<br>Line sync mode enable<br>Bit[3]: lp_sst_en                                                                                                          |

## 2.6.2 D\_PHY related register configuration

table 2-5 D\_PHY related registers

| address | register name                                            | default value | R/W | description                                                                                                              |

|---------|----------------------------------------------------------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------|

| P0:0x44 | MP_DA_SSEL,<br>MP_CLK_SSEL,<br>MP_PHASE_INV,<br>MP_PHASE | 0x05          | RW  | Bit[6]: mp_da_ssel<br>Bit[5]: mp_clk_ssel<br>Bit[4]: mp_phase_inv<br>DPHY DDR clock phase inverted<br>Bit[3:0]: mp_phase |

| P1:0x9D | HS_LEV                                                   | 0x15          | RW  | Bit[6:0]: hs_lev<br>Adjust high speed output<br>difference mode voltage range<br>and HS maximum value                    |

| P1:0x9E | HS_DRV                                                   | 0x55          | RW  | Bit[7:0]: hs_drv                                                                                                         |

## 2.7 reset

The whole chip will be reset during power up. Manually applying a hard reset (RSTN = 0) upon power-up is recommended even through an on-chip power on reset is included. The hard reset (RSTN) is active low with an asynchronous design. The reset pulse width should be no less than 2 ms.

### 2.7.1 power on reset generation

The OS02G10 includes a RSTN pin that forces a complete hardware reset when it is pulled low (GND). Additionally, a power on reset (POR) is generated after core power becomes stable. The OS02G10 clears all registers to their default values.

### 2.7.2 software reset

A reset can also be initiated via the SCCB interface by writing P0:0x20 = 0x00. Then, all registers will be reset to their default values.

## 2.8 system clock control

### 2.8.1 MPLL (MIPI\_PLL)

PLL1 generates a default 84 MHz pixel clock and an 840 MHz MIPI serial clock from a 10~36 MHz input clock. The VCO range is from 400 MHz to 940 MHz. A programmable clock divider is provided to generate different frequencies.

### 2.8.2 clock configuration

table 2-6      clock configuration related registers (sheet 1 of 2)

| address | register name                               | default value | R/W | description                                                                                                                                                                                        |

|---------|---------------------------------------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0:0x2F | MPLL_MC                                     | 0x01          | RW  | <p>Bit[7:0]: mpll_mc<br/>           PLL output = [PLL input * (2- mpll_nc[7])<br/>           (mpll_nc[6:0]+3)/(mpll_mc+1)]</p> <p>Note: Parameters of registers will be enabled in next frame.</p> |

| P0:0x30 | DPLL_CP_DIV,<br>PLL_DACCLK_DIV,<br>MPLL_DIV | 0x02          | RW  | <p>Bit[5:4]: dpll_cp_div<br/>           Bit[3:2]: dpll_dacclk_div<br/>           Bit[1:0]: mpll_div</p>                                                                                            |

table 2-6      clock configuration related registers (sheet 2 of 2)

| address | register name                | default value | R/W | description                                                                                                                                                                                                                                            |

|---------|------------------------------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0:0x31 | CLK_MODE_BUF                 | 0x11          | RW  | <p>Bit[7]: pclk_ctrl<br/>0: PCLK = pll_clk<br/>1: PCLK = 1/2 pll_clk</p> <p>Bit[4]: row_clk_ctrl<br/>0: row_clk = timer_clk<br/>1: row_clk = 1/2 timer_clk</p> <p>Bit[0]: timer_clk_ctrl<br/>0: timer_clk = pll_clk<br/>1: timer_clk = 1/2 pll_clk</p> |

|         |                              |               |     | Note: Parameters of registers will be enabled in next frame.                                                                                                                                                                                           |

| P0:0x38 | PCLK_GATE_EN,<br>PLL_GATE_EN | 0x01          | RW  | <p>Bit[4]: pclk_gate_en<br/>Pad PCLK gating enable signal<br/>0: Disable PCLK gating<br/>1: Enable PCLK gating</p> <p>Bit[0]: pll_gate_en<br/>PLL gating enable signal<br/>0: Enable PLL gating<br/>1: Disable PLL gating</p>                          |

| P0:0x43 | MP_RAW_SEL,<br>MP_DOUBLE     | 0x01          | RW  | <p>Bit[2:1]: mp_raw_sel<br/>MIPI RAW select<br/>00: RAW10 /10<br/>01: RAW8 /8<br/>10: RAW12 /12<br/>11: Disable timer_clk output</p> <p>Bit[0]: mp_double</p>                                                                                          |

| P0:0x45 | DPLL_SEL                     | 0x00          | RW  | <p>Bit[0]: dpll_sel<br/>Bypass loop for DAC clock</p>                                                                                                                                                                                                  |

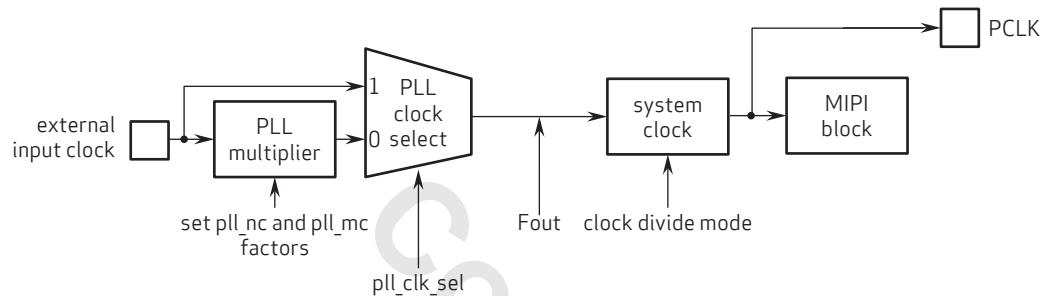

### 2.8.3 PLL clock scheme

The OS02G10 contains a phase locked loop (PLL) block, which generates all the necessary internal clocks from an external clock input. The internal function blocks of the PLL are shown in [figure 2-4](#).

[figure 2-4](#) PLL internal function block diagram

**note**  $F_{out} = F_{in} * \frac{(2 - mpill\_mc[7]) \times (mpill\_nc[6:0] + 3)}{(mpill\_mc[2:0] + 1)}$  is in range of 400 MHz to 940 MHz

## 2.9 power management

In power down mode, all internal clocks are stopped and all sensor modules are powered off. The register values will all be reset in power down mode.

In soft reset mode, all register values will be reset, but all internal clocks are kept and all sensor modules work normally.

In low power wake mode, all internal clocks are stopped and all sensor modules are powered off. The register values will all be kept in low power wake mode.

## 2.10 data lane parameters

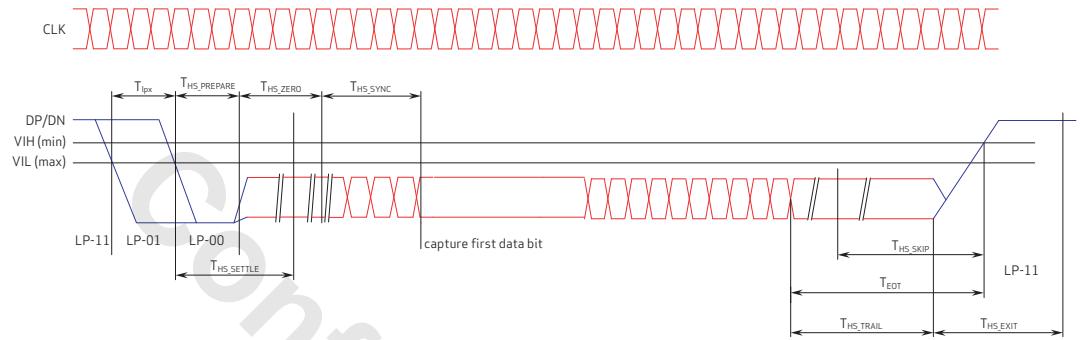

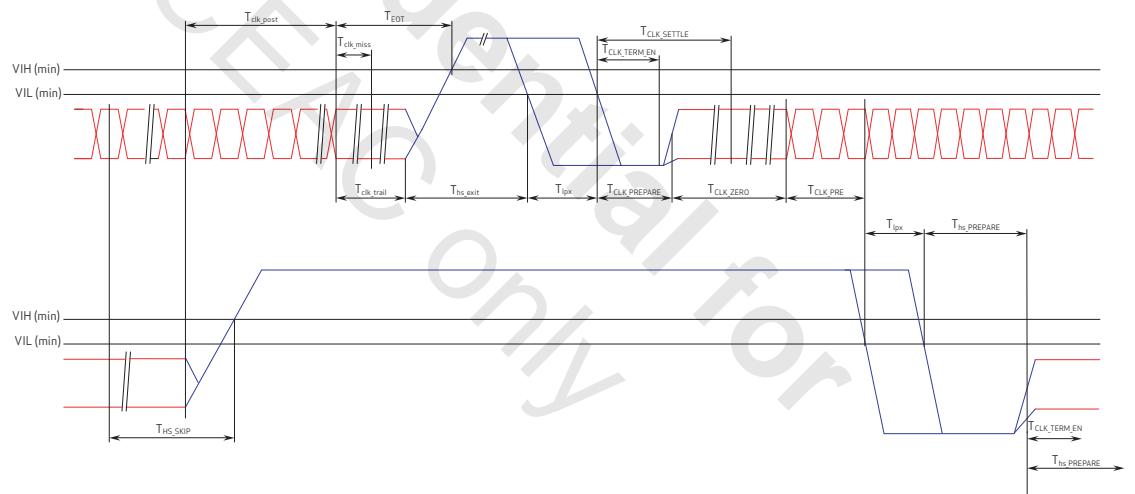

The D-PHY converts parallel data from CSI\_TOP to serial data that is compatible with MIPI protocol. Detailed time sequences are shown in [figure 2-5](#) and [figure 2-6](#).

[figure 2-5](#) high-speed data transmission bursts

[figure 2-6](#) switching the clock lane between clock transmission and low-power mode

table 2-7 data lane parameters

| parameter                      | target                                                                                                                                                                        | min                             | max            |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|

| $T_{HS-PREPARE}$               | time that transmitter drives data lane LP-00 line state immediately before HS-0 Line state starts HS transmission                                                             | 40 ns + 4*UI                    | 85 ns + 6*UI   |

| $T_{HS-PREPARE} + T_{HS-ZERO}$ | $T_{HS-PREPARE} +$ time that transmitter drives HS-0 state prior to transmitting sync sequence                                                                                | 145 ns + 10*UI                  |                |

| $T_{HS-SETTLE}$                | time interval which HS receive shall ignore any data lane HS transitions, starting from beginning of $T_{HS-PREPARE}$                                                         | 85 ns + 6*UI                    | 145 ns + 10*UI |

| $T_{HS-SKIP}$                  | time interval which HS-RX should ignore any transitions on data lane, following a HS burst<br>end point of interval is defined as beginning of LP-11 state following HS burst | 40 ns                           | 55 ns + 4*UI   |

| $T_{HS-TRAIL}$                 | time that transmitter drives HS-0 state after last payload clock bit of a HS transmission burst                                                                               | max (n*8*UI,<br>60 ns + n*4*UI) |                |

| $T_{LPX}$                      | transmitted length of any low-power state period                                                                                                                              | 50 ns                           |                |

| $T_{WAKEUP}$                   | time that a transmitter drives a Mark-1 state prior to a stop state in order to initiate an exit from ULPS                                                                    | 1 ms                            |                |

## 2.11 clock lane parameters

table 2-8      clock lane parameters

| parameter                        | target                                                                                                                                                                                             | min                 | max    |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|

| $T_{CLK-MISS}$                   | timeout for receiver to detect absence of clock transmission and disable clock lane HS-RX                                                                                                          | 60 ns               |        |

| $T_{CLK-POST}$                   | time that transmitter continues to send HS clock after last associated data lane has transitioned to LP mode interval is defined as period from end of $T_{HS-TRAIL}$ to beginning $T_{CLK-TRAIL}$ | 60 ns + 52*UI       |        |

| $T_{CLK-PRE}$                    | time that HS clock will be driven by transmitter prior to any associated data lane beginning transition from LP to HS mode                                                                         | 8*UI                |        |

| $T_{CLK-PREPARE}$                | time that transmitter drives clock lane LP-00 line state immediately before HS-0 line state starts HS transmission                                                                                 | 38 ns               | 95 ns  |

| $T_{CLK-SETTLE}$                 | time interval which HS receive will ignore any clock lane HS transmissions, starting from beginning of $T_{CLK-PREPARE}$                                                                           | 95 ns               | 300 ns |

| $T_{CLK-TRAIL}$                  | time that transmitter drives HS-0 state after last payload clock bit of a HS transmission burst                                                                                                    | 60 ns               |        |

| $T_{CLK-PREPARE} + T_{CLK-ZERO}$ | $T_{CLK-PREPARE} +$ time that transmitter drives HS-0 state prior to starting clock                                                                                                                | 300 ns              |        |

| $T_{EOT}$                        | transmitted time interval from start of $T_{CLK-TRAIL}$ or $T_{HS-TRAIL}$ , to start of LP-11 state following a HS burst                                                                           | 105 ns +<br>n*12*UI |        |

## 2.12 power up/off sequence

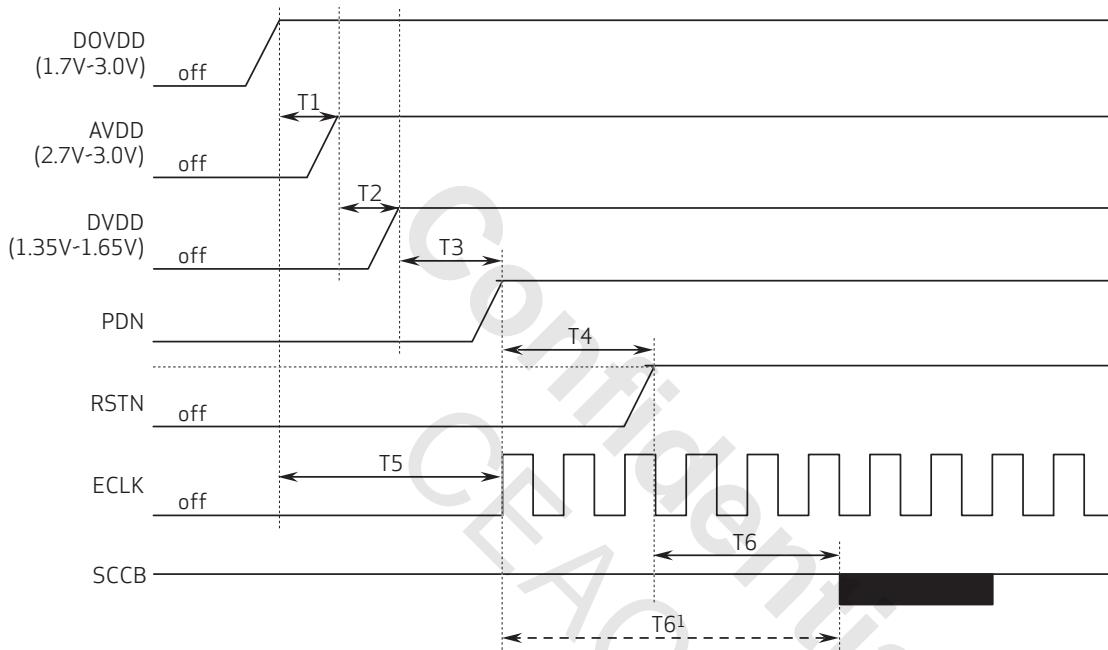

### 2.12.1 power up sequence

figure 2-7 power up sequence diagram

table 2-9 power up sequence parameters

| symbol          | description                                                                                                         | min | unit |

|-----------------|---------------------------------------------------------------------------------------------------------------------|-----|------|

| T1              | delay from DOVDD to AVDD                                                                                            | 0   | ms   |

| T2              | delay from AVDD to DVDD                                                                                             | 0   | ms   |

| T3              | delay from DVDD stable to sensor power up stable                                                                    | 5   | ms   |

| T4              | delay from sensor power up stable to RSTN pull up                                                                   | 4   | ms   |

| T5              | delay from DOVDD stable to ECLK on                                                                                  | 0   | ms   |

| T6              | delay from sensor power up stable to SCCB initialization                                                            | 5   | ms   |

| T6 <sup>1</sup> | RSTN signal remains high at any time<br>T6 <sup>1</sup> = T4 + T6, T6 <sup>1</sup> starts at sensor power up stable | 9   | ms   |

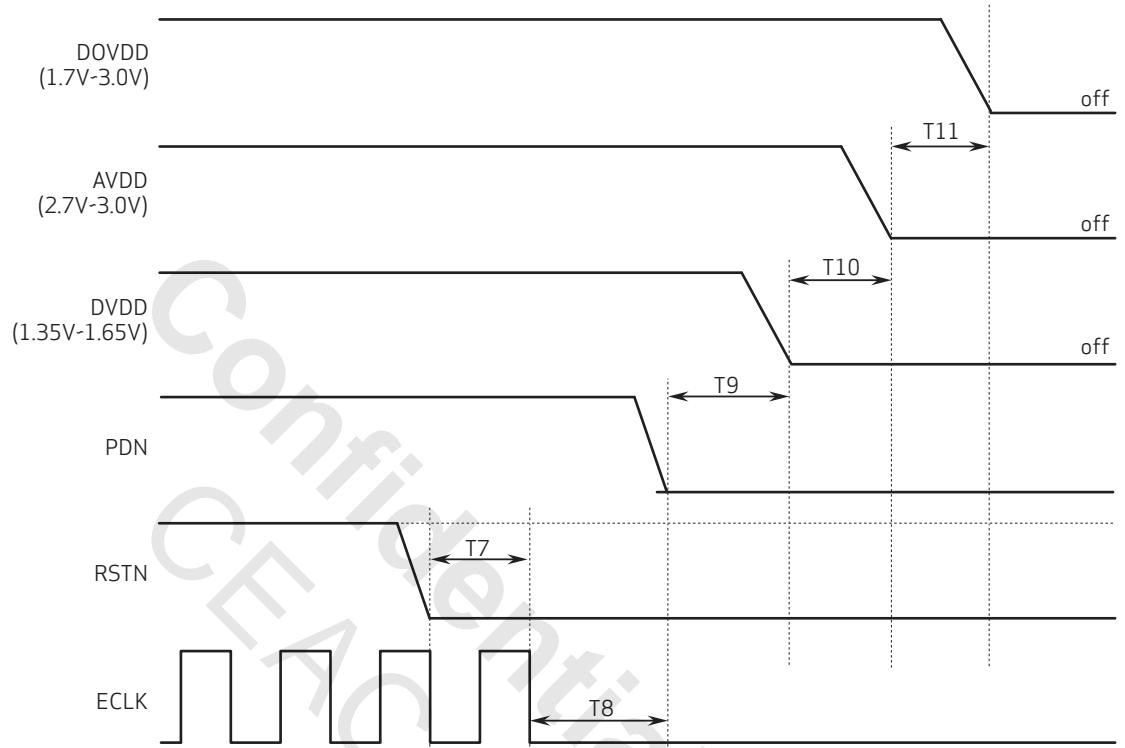

## 2.12.2 power off sequence

figure 2-8 power off sequence diagram

table 2-10 power off sequence parameters

| symbol | description                                 | min | unit |

|--------|---------------------------------------------|-----|------|

| T7     | delay from RSTN pull low stable to ECLK off | 0   | ms   |

| T8     | delay from ECLK off to sensor power down    | 0   | ms   |

| T9     | delay from sensor power down to DVDD off    | 0   | ms   |

| T10    | delay from DVDD off to AVDD off             | 0   | ms   |

| T11    | delay from AVDD off to DOVDD off            | 0   | ms   |

## 2.13 SCCB bus

### 2.13.1 single read and single write

The OS02G10 SCCB write address and read address can be selected by the SID pin. When the pin is set high, the write address is 0x7A and the read address is 0x7B. When the pin is set low, the write address is 0x78 and the read address is 0x79.

A typical read or write sequence begins by the master sending a start bit. After the start bit, the master sends the slave device's 8-bit address. The last bit of the address determines if the request will be a read or a write, where a '0' indicates a write and a '1' indicates a read. The slave device acknowledges its address by sending an acknowledge bit back to the master.

If the request was a write, the master then transfers the 8-bit register address to which a write should take place. The slave sends an acknowledge bit to indicate that the register address has been received. The master then transfers the data 8 bits at a time, with the slave sending an acknowledge bit after each 8 bits. The master stops writing by sending a start or stop bit.

A typical read sequence is executed as follows. First, the master sends the write-mode slave address and 8-bit register address just as in the write request. The master then sends a start bit and the read-mode slave address. The master then clocks out the register data 8 bits at a time. The master sends an acknowledge bit after each 8-bit transfer. The data transfer is stopped when the master sends a no-acknowledge bit.

**figure 2-9** illustrates the OS02G10 single read sequence and single write sequence.

**figure 2-9** SCCB read and write message description (SID pin set high)

**figure 2-10** SCCB read and write message description (SID pin set low)

### 2.13.2 data bit transfer

One data bit is transferred during each clock pulse. The serial clock pulse is provided by the master. The data must be stable during the high period of the serial clock. It can only change when the serial clock is low. Data is transferred 8 bits at a time, followed by an acknowledge bit.

### 2.13.3 acknowledge bit

The OS02G10 will hold the value of the SDA pin to logic '0' during the logic '1' state of the acknowledge clock pulse on SCL.

**figure 2-11** SCCB acknowledge bit diagram

### 2.13.4 data valid

The master must ensure that the data is stable during the logic 1 state of the SCL pin. All transitions on the SDA pin can only occur when the logic level on the SCL pin is '0'.

**figure 2-12** SCCB data transport diagram

### 2.13.5 timing parameter

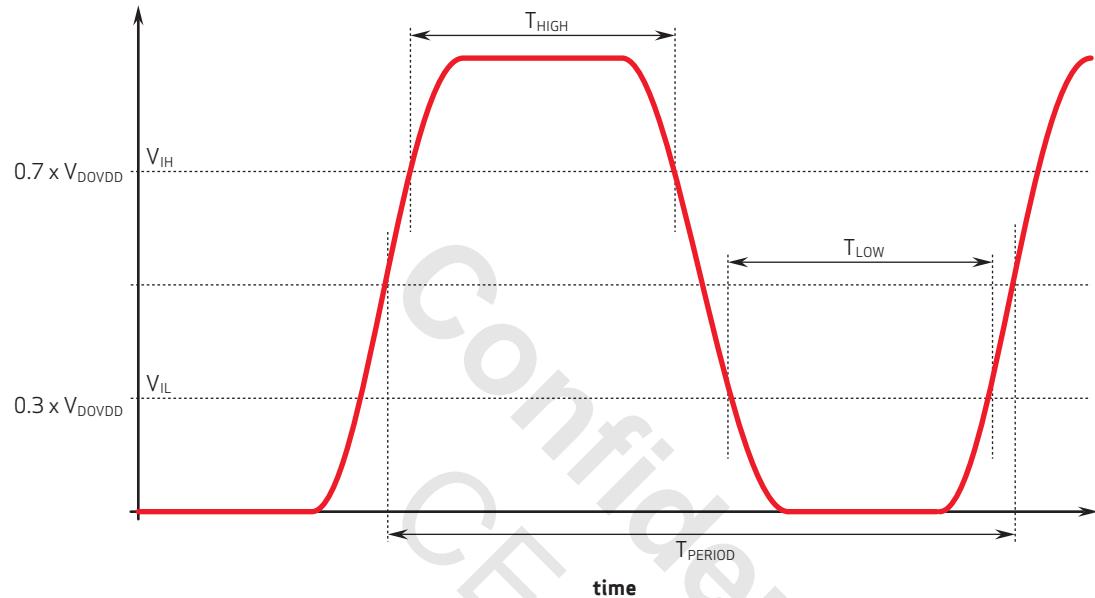

figure 2-13 SCCB bus timing parameter diagram

table 2-11 SCCB interface timing specifications

| symbol        | parameter                                | min | max | unit    |

|---------------|------------------------------------------|-----|-----|---------|

| $f_{scl}$     | SCL clock frequency                      | —   | 400 | kHz     |

| $t_{buf}$     | bus free time between a stop and a start | 1.3 | —   | $\mu$ s |

| $t_{hd\_sta}$ | hold time for a repeated start           | 0.6 | —   | $\mu$ s |

| $t_{low}$     | low period of SCL                        | 1.3 | —   | $\mu$ s |

| $t_{high}$    | high period of SCL                       | 0.6 | —   | $\mu$ s |

| $t_{su\_sta}$ | setup time for a repeated start          | 0.6 | —   | $\mu$ s |

| $t_{hd\_dat}$ | data hold time                           | 0   | —   | $\mu$ s |

| $t_{su\_dat}$ | data setup time                          | 0.1 | —   | $\mu$ s |

| $t_r$         | rise time of SCL, SDA                    | —   | 0.3 | $\mu$ s |

| $t_f$         | fall time of SCL, SDA                    | —   | 0.1 | $\mu$ s |

| $t_{su\_sto}$ | setup time for a stop                    | 0.6 | —   | $\mu$ s |

| $t_{aa}$      | SCL low to data out valid                | 0.3 | —   | $\mu$ s |

| $t_{dh}$      | data out hold time                       | 0.2 | —   | $\mu$ s |

| $C_b$         | capacitive load of bus line (SCL, SDA)   | —   | —   | pf      |

OS02G10

color CMOS 2 megapixel image sensor

Confidential for

CEAC only

## 3 block level description

### 3.1 pixel array structure

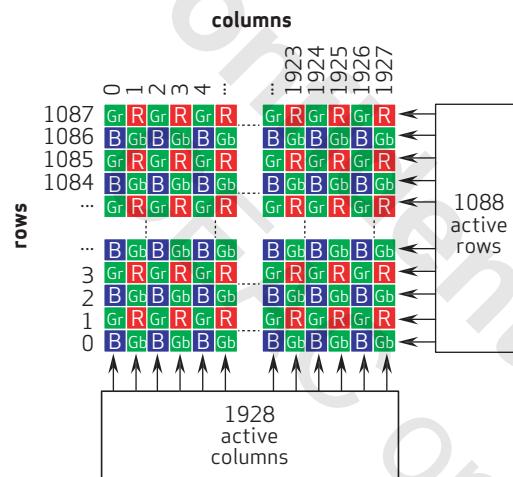

The OS02G10 sensor has an image array of 1928 columns by 1088 rows (2,097,664 pixels). **figure 3-1** shows a cross-section of the image sensor array.

The color filters are arranged in a Bayer pattern. The primary color GR/BG array is arranged in line-alternating fashion. Of the 2,162,944 pixels, 2,073,600 (1920x1080) are active pixels and can be output.

The sensor array design is based on a field integration readout system with line-by-line transfer and an electronic shutter with a synchronous pixel readout scheme.

**figure 3-1** sensor array region color filter layout

### 3.2 binning

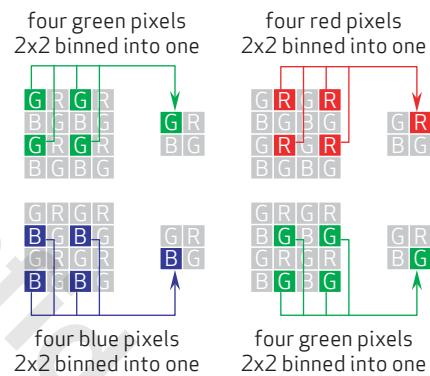

The OS02G10 supports a binning mode to provide a lower resolution output while maintaining the field of view. With binning mode on, the voltage levels of adjacent pixels (of the same color) are averaged. The OS02G10 supports 2x2 binning, which is illustrated in **figure 3-2**, where the voltage levels of two horizontal (2x1) adjacent same-color pixels are averaged.

**figure 3-2** example of 2x2 binning

**table 3-1** binning-related register

| address | register name | default value | R/W | description                                                                                                                           |

|---------|---------------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| P1:0x31 | COMM_CTRL     | 0x00          | RW  | <p>Bit[4]: bypass_dsp</p> <p>Bit[3]: binning_en</p> <p>Bit[2]: v_binning_en</p> <p>Bit[1]: mode_720p</p> <p>Bit[0]: ana_window_en</p> |

## 4 image sensor core digital functions

### 4.1 mirror and flip

The OS02G10 provides mirror and flip readout modes, which respectively reverse the sensor data readout order horizontally and vertically (see **figure 4-1**).

**figure 4-1** mirror and flip samples

**table 4-1** mirror and flip registers

| address | register name | default value | R/W | description                                                                                                 |

|---------|---------------|---------------|-----|-------------------------------------------------------------------------------------------------------------|

| P1:0x3F | FLIP/MIRROR   | 0x00          | RW  | <p>Bit[1:0]: Flip/mirror</p> <p>00: Normal</p> <p>01: Mirror</p> <p>10: Flip</p> <p>11: Mirror and flip</p> |

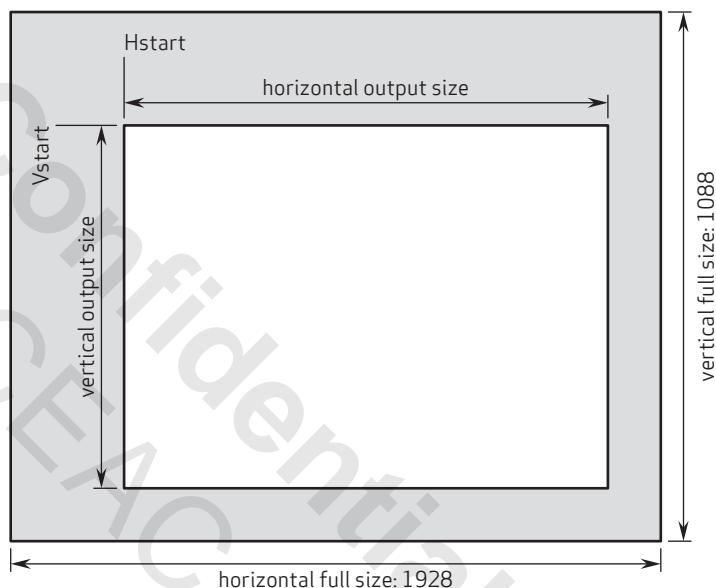

## 4.2 windowing

The embedded windowing function extracts an image windowing area by defining four parameters, including horizontal start, horizontal width, vertical start, and vertical height. By properly setting the parameters, the portions within the sensor array size can be cropped as a visible area. The windowing function will not conflict with the mirror and flip function as shown in [figure 4-2](#).

[figure 4-2](#) windowing diagram

[table 4-2](#) windowing control registers (sheet 1 of 2)

| address | register name                                      | default value | R/W | description                                                                                 |

|---------|----------------------------------------------------|---------------|-----|---------------------------------------------------------------------------------------------|

| P1:0x34 | COL_ANA_ADDR_START_2MSB,<br>COL_ANA_ADDR_SIZE_2MSB | 0x00          | RW  | Bit[5:4]: Col_ana_addr_size_2msb<br>Bit[3:2]: Not used<br>Bit[1:0]: Col_ana_addr_start_2msb |

| P1:0x35 | COL_ANA_ADDR_START_8LSB                            | 0x00          | RW  | Bit[7:0]: Col_ana_addr_start_8lsb                                                           |

| P1:0x36 | COL_ANA_ADDR_SIZE_8LSB                             | 0x03          | RW  | Bit[7:0]: Col_ana_addr_size_8lsb                                                            |

| P1:0x4A | VSTART_3MSB                                        | 0x00          | RW  | Bit[2:0]: VSTART[10:8]                                                                      |

| P1:0x4B | VSTART_8LSB                                        | 0x00          | RW  | Bit[7:0]: VSTART[7:0]                                                                       |

**table 4-2** windowing control registers (sheet 2 of 2)

| address | register name | default value | R/W | description           |

|---------|---------------|---------------|-----|-----------------------|

| P1:0x4C | VSIZE_3MSB    | 0x04          | RW  | Bit[2:0]: VSIZE[10:8] |

| P1:0x4D | VSIZE_8LSB    | 0x40          | RW  | Bit[7:0]: VSIZE[7:0]  |

### 4.3 test pattern

Test pattern and color bar are offered for testing purposes.

**figure 4-3** test pattern diagram

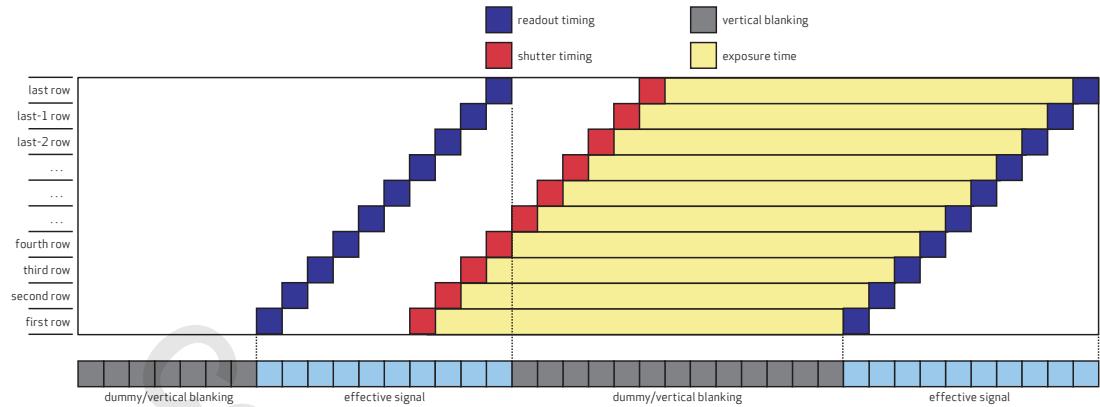

### 4.4 shutter and integration time settings and continuous exposure control

The OS02G10 has a variable electronic shutter function that can control the integration time in row units. In addition, the OS02G10 performs rolling shutter operation in which electronic shutter and readout are performed sequentially for each row.

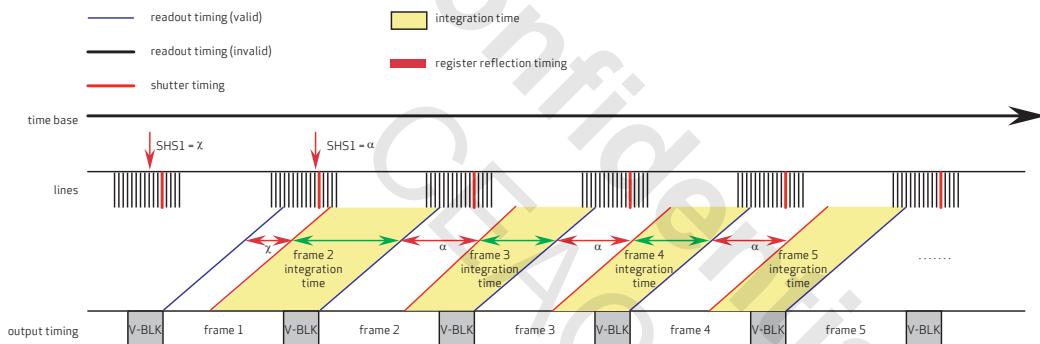

figure 4-4 shutter and integration time settings and continuous exposure control

The integration time can be controlled by varying the electronic shutter time. In the electronic shutter setting, the integration time is controlled by the EXP register ({P1:0x03, P1:0x04}).

#### 4.4.1 exposure/gain control

The OS02G10 exposure registers are P1:0x03 and P1:0x04. The unit is Tline. Minimum exposure is 4 Tline. The maximum exposure is VTS-8. If the exposure is longer than VTS-8, the OS02G10 will automatically prolong the current VTS. To disable the VTS auto prolong feature, enable P1:0x0D[4] for manual VTS.

After registers P1:0x03 and P1:0x04 are set, register P1:0x01 must be set to 0x01 to trigger the new exposure.

The OS02G10 supports AGC gain. The AGC gain register is P1:0x24, 0x10 is 1x. Maximum AGC gain is 0xF8 = 15.5x. The AGC gain also needs register P1:0x01 to be set to 0x01 to trigger it.

The OS02G10 supports digital gain. The digital gain registers are P1:0x37 and P1:0x39. P1:0x39 = 0x40 is 1x digital gain. Maximum digital gain is (P1:0x37 = 0x07, P1:0x39 = 0xFF) = 32x. The minimum step is 1/64. The digital gain also needs register P1:0x01 to be set to 0x01 to trigger it. An example setting for exposure/AGC gain/digital gain control is shown below:

```

78 FD 01

78 03 01

78 04 54      ;exposure time 0x154

78 24 80      ;AGC gain 8x

78 39 80      ;digital gain 2x

78 01 01      ;trigger the new exposure/gain

```

The new exposure/AGC gain/digital gain will be valid after next frame.

#### 4.4.2 HTS/VTS

The HTS/VTS registers are read only registers. Registers P1:0x41 and P1:0x42 are HTS registers. The unit is timer\_clk. Registers P1:0x4E and P1:0x4F are VTS registers. The unit is Tline. To modify VTS, insert dummy lines with registers

P1:0x05 and P1:0x06. Register P1:0x01 must be set to 0x01 to trigger the new Vblank. Registers P1:0x05 and P1:0x06 are Vblank registers. Registers P1:0x09 and P1:0x0A are Hblank registers.

For example, if the current dummy line is 1 line (P1:0x05 = 0x00 and P1:0x06 = 0x01) and the user wants to insert 16 dummy lines, the following setting is recommended:

```

78 FD 01

78 05 00

78 06 11      ;new dummy line

78 01 01

```

It is not recommended to change the HTS. If a change to the HTS is desired, please contact the local OmniVision FAE for support.

**figure 4-5** integration time control within a frame

## 4.5 FSIN

Data output of the OS02G10 can be synchronized. The OS02G10 can be either a master or slave device in FSIN mode. After synchronization, the time difference between the data output of master and slave is less than 1H.

## 4.5.1 FSIN common control

table 4-3 FSIN control registers

| address | register name                   | default value | R/W | description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------------------------------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0:0x40 | EXT_SYNC_MST_EN,<br>EXT_SYNC_EN | 0x00          | RW  | <p>Bit[1]: ext_sync_mst_en<br/>Enable master mode of external sync function<br/>0: OS02G10 is slave of external sync<br/>1: OS02G10 is master of external sync</p> <p>Bit[0]: ext_sync_en<br/>Enable signal of external sync function<br/>0: Disable external sync<br/>1: Enable external sync</p>                                                                                                                                                                                                                                                                                                                                                                  |

| P1:0x0B | EXTER_SYNC_CTL                  | 0x00          | RW  | <p>Bit[7]: exter_sync_inv<br/>Bit[6]: exter_frame_num_x256_en<br/>When enabled, 1 LSB of exter_sync_frame_num (P1:0x17) equals 256 frames<br/>0: Disable<br/>1: Enable</p> <p>Bit[5]: exter_del_en<br/>0: Disable<br/>1: Enable</p> <p>Bit[4]: exter_sync_manual_en<br/>Configure a posedge in this bit to trigger a sync output in master mode</p> <p>Bit[3]: exter_sync_auto_en<br/>Sensor in master mode will send sync signal every exter_sync_frame_num (P1:0x17) frames automatically<br/>0: Disable<br/>1: Enable</p> <p>Bit[2]: sync_no_wait_en<br/>Bit[1]: External sync slave mode<br/>Bit[0]: External sync master mode<br/>0: Disable<br/>1: Enable</p> |

| P1:0x15 | EXP_SYNC_FRAME_NUM              | 0x0A          | RW  | Bit[7:0]: Interval frame number of auto external frame synchronize pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

The master/slave mode, IE, OE, input polarity, output polarity, and input filter settings are programmed by register P0:0x1B.

## 4.6 auto black level calibration (ABLC)

The OS02G10 pixel array contains eight shielded (optical black) rows, among which 8/4 rows are used for black level calibration automatically. The whole ABLC process consists of three stages: black level obtained by averaging optical black rows, black level taking effect by triggers, and black level calibration.

### 4.6.1 obtaining black level

Several functions can be tuned during the process of obtaining black level.

The effective black level and current frame black level values can be read out by register. The readout data contains four decimals. Without trigger mode, the following data can be still read out.

Offset is a signed number, the range is -256~255.

**table 4-4 BLC registers**

| address | register name           | default value | R/W | description                                                    |

|---------|-------------------------|---------------|-----|----------------------------------------------------------------|

| P1:0xDD | BLC_BLACK_LEVEL_Gb_8MSB | –             | R   | Bit[7:0]: black_level_gb[15:8]<br>Effective Gb black level MSB |

| P1:0xDE | BLC_BLACK_LEVEL_B_8MSB  | –             | R   | Bit[7:0]: black_level_b[15:8]<br>Effective B black level MSB   |

| P1:0xDF | BLC_BLACK_LEVEL_R_8MSB  | –             | R   | Bit[7:0]: black_level_r[15:8]<br>Effective R black level MSB   |

| P1:0xE0 | BLC_BLACK_LEVEL_GR_8MSB | –             | R   | Bit[7:0]: black_level_gr[15:8]<br>Effective Gr black level MSB |

| P1:0xE1 | BLC_BLACK_LEVEL_Gb_8LSB | –             | R   | Bit[7:0]: black_level_gb[7:0]<br>Effective Gb black level LSB  |

| P1:0xE2 | BLC_BLACK_LEVEL_B_8LSB  | –             | R   | Bit[7:0]: black_level_b[7:0]<br>Effective B black level LSB    |

| P1:0xE3 | BLC_BLACK_LEVEL_R_8LSB  | –             | R   | Bit[7:0]: black_level_r[7:0]<br>Effective R black level LSB    |

| P1:0xE4 | BLC_BLACK_LEVEL_GR_8LSB | –             | R   | Bit[7:0]: black_level_gr[7:0]<br>Effective Gr black level LSB  |

#### 4.6.2 trigger mode

Black level statistics are always calculated in real time. The OS02G10 supports the following trigger modes:

**table 4-5 BLC statistics register**

| address | register name | default value | R/W | description                                                                                                                                                                                                                                         |

|---------|---------------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1:0xFA | ABL_TRIGGER   | 0x00          | RW  | <p>Bit[7]: Manual function<br/>Use with bit[0] at same time</p> <p>Bit[5]: Auto BLC enable</p> <p>Bit[4]: RPC function</p> <p>Bit[3]: Exp function</p> <p>Bit[2]: Mean function</p> <p>Bit[1]: frame_count reset</p> <p>Bit[0]: Manual function</p> |

Offset is a signed number, the range is -256~255.

**table 4-6 BLC offset registers (sheet 1 of 2)**

| address | register name  | default value | R/W | description                                                                                                                                                                |

|---------|----------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1:0xF0 | GB_SUBOFFSET   | 0x00          | RW  | <p>Bit[7:0]: Blacklevel offset, Gb channel, low 8 bits</p> <p>Total register is 9 bits with MSB at P1:0xF8[7] (-256~255, 0x100~0x0FF)</p> <p>Highest bit is sign bit</p>   |

| P1:0xF1 | BLUE_SUBOFFSET | 0x00          | RW  | <p>Bit[7:0]: Blacklevel offset, blue channel, low 8 bits</p> <p>Total register is 9 bits with MSB at P1:0xF8[6] (-256~255, 0x100~0x0FF)</p> <p>Highest bit is sign bit</p> |

| P1:0xF2 | RED_SUBOFFSET  | 0x00          | RW  | <p>Bit[7:0]: Blacklevel offset, red channel, low 8 bits</p> <p>Total register is 9 bits with MSB at P1:0xF8[5] (-256~255, 0x100~0x0FF)</p> <p>Highest bit is sign bit</p>  |

| P1:0xF3 | GR_SUBOFFSET   | 0x00          | RW  | <p>Bit[7:0]: Blacklevel offset, Gr channel, low 8 bits</p> <p>Total register is 9 bits with MSB at P1:0xF8[4] (-256~255, 0x100~0x0FF)</p> <p>Highest bit is sign bit</p>   |

**table 4-6** BLC offset registers (sheet 2 of 2)

| address | register name                                                                      | default value | R/W | description                                                                                                 |